2021-09-03 23:18:08 索炜达电子 1116

项目编号:E774

文件大小:113K

源码说明:带中文注释

开发环境:Verilog

简要概述:

用verilog实现minst 的数字识别, 可以用modelsim看结果, 如果要部署到fpga上, PL的资源要非常非常多

代码下载:(包含5个仿真文件)

以数字2的仿真文件为例, 可以显示以下的结果,因为最终0-9里 数字2的得分最高,所以判断是2, 这里只是要判断最有可能的数字, 就不再化成几率的形式了

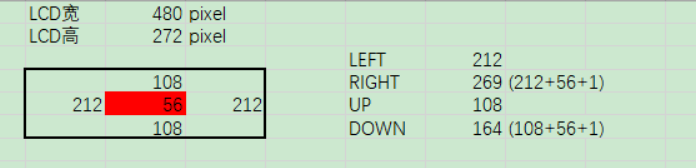

代码里的x坐标和y坐标,是假设在480*272的lcd上显示, 因为minst的像素是28*28的.我们假每4个LCD的像素点代表minst的一个点,那就是在中间红色的区域才是数字显示的区域

目录│文件列表:

└ verilog_mnist-main

└ verilog_mnist-main

│ digital_recognition.v

│ myram_28X28.v

│ tb_result1_2x2.v

│ tb_result2_2x2.v

│ tb_result4_2x2.v

│ tb_result7_2x2.v

└ tb_result9_2x2.v