2021-09-05 09:16:32 索炜达电子 812

项目编号:E787

文件大小:4.8M

源码说明:带中文注释

开发环境:Verilog

简要概述:

简要概述:

Altera公司的三速以太网(TSE)是一个可配置的FPGA软核MAC,主要应用于10/100 Mbps (快速以太网)和1000 Mbps (千兆以太网)线路卡、NIC卡以及交换机等。

官方资源:

http://www.altera.com.cn/support/ip/interface-protocols/ips-inp-tse.html

http://www.altera.com.cn/literature/ug/ug_ethernet.pdf

http://www.altera.com.cn/support/refdesigns/ip/interface/ref-triple-speed-ethernet-data-path.html

http://www.altera.com.cn/literature/an/an647.pdf

http://www.altera.com.cn/literature/an/an440.pdf

http://www.altera.com.cn/literature/an/an483.pdf

http://www.altera.com/support/ip/interface-protocols/ips-inp-tse.html

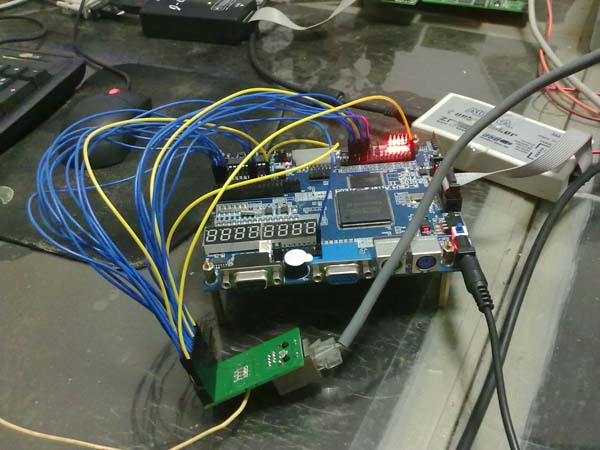

官方的FPGA开发套件提供了与Marvell 88E1111 PHY工作的实例,但俺没有银子,最便宜的DE2开发板也得3000块吧。我用手头的EP2C8Q208C8搭建了一个测试平台:

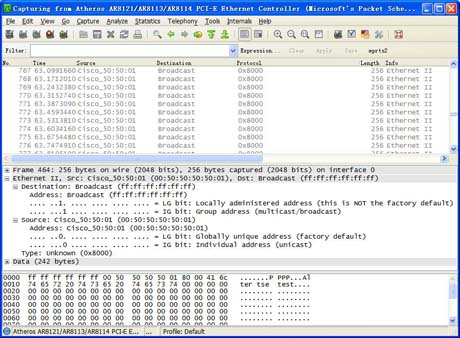

(1)发送测试:

(2)接收测试:

Id1 = 0x13, Id2 = 0x78e2.

Wait reset.

Reset ok.

config = 0x3100.

MII status = 0x7809.

Reg 4 = 0x1e1.

Wait Auto-nego...OK.

config = 0x3100.

MII status = 0x782d.

MII status2 = 0x4780.

Link OK.

-----------------------------

RX 0x3c bytes:

0000: FF FF FF FF FF FF 00 25 11 06 07 39 08 06 00 01

0010: 08 00 06 04 00 01 00 25 11 06 07 39 C0 A8 01 A0

0020: 00 00 00 00 00 00 C0 A8 01 79 00 00 00 00 00 00

0030: 00 00 00 00 00 00 00 00 00 00 00 00

-----------------------------

RX 0x3c bytes:

0000: FF FF FF FF FF FF 00 25 11 06 07 39 08 06 00 01

0010: 08 00 06 04 00 01 00 25 11 06 07 39 C0 A8 01 A0

0020: 00 00 00 00 00 00 C0 A8 01 79 00 00 00 00 00 00

0030: 00 00 00 00 00 00 00 00 00 00 00 00

-----------------------------

RX 0x3c bytes:

0000: FF FF FF FF FF FF 00 25 11 06 07 39 08 06 00 01

0010: 08 00 06 04 00 01 00 25 11 06 07 39 C0 A8 01 A0

0020: 00 00 00 00 00 00 C0 A8 01 79 00 00 00 00 00 00

0030: 00 00 00 00 00 00 00 00 00 00 00 00

-----------------------------

RX 0x3c bytes:

0000: FF FF FF FF FF FF 00 25 11 06 07 39 08 06 00 01

0010: 08 00 06 04 00 01 00 25 11 06 07 39 C0 A8 01 A0

0020: 00 00 00 00 00 00 C0 A8 01 79 00 00 00 00 00 00

0030: 00 00 00 00 00 00 00 00 00 00 00 00

-----------------------------

RX 0x5c bytes:

0000: FF FF FF FF FF FF 00 25 11 06 07 39 08 00 45 00

0010: 00 4E 10 76 00 00 40 11 E5 39 C0 A8 01 A0 C0 A8

0020: 01 FF 00 89 00 89 00 3A AA 2E 80 D7 01 10 00 01

0030: 00 00 00 00 00 00 20 45 44 45 42 45 4A 46 48 46

0040: 46 43 41 43 41 43 41 43 41 43 41 43 41 43 41 43

0050: 41 43 41 43 41 43 41 00 00 20 00 01

-----------------------------

RX 0x5c bytes:

0000: FF FF FF FF FF FF 00 25 11 06 07 39 08 00 45 00

0010: 00 4E 10 86 00 00 40 11 E5 29 C0 A8 01 A0 C0 A8

0020: 01 FF 00 89 00 89 00 3A AA 2E 80 D7 01 10 00 01

0030: 00 00 00 00 00 00 20 45 44 45 42 45 4A 46 48 46

0040: 46 43 41 43 41 43 41 43 41 43 41 43 41 43 41 43

0050: 41 43 41 43 41 43 41 00 00 20 00 01

-----------------------------

RX 0x5c bytes:

0000: FF FF FF FF FF FF 00 25 11 06 07 39 08 00 45 00

0010: 00 4E 10 95 00 00 40 11 E5 1A C0 A8 01 A0 C0 A8

0020: 01 FF 00 89 00 89 00 3A AA 2E 80 D7 01 10 00 01

0030: 00 00 00 00 00 00 20 45 44 45 42 45 4A 46 48 46

0040: 46 43 41 43 41 43 41 43 41 43 41 43 41 43 41 43

0050: 41 43 41 43 41 43 41 00 00 20 00 01

-----------------------------

RX 0x5c bytes:

0000: FF FF FF FF FF FF 00 25 11 06 07 39 08 00 45 00

0010: 00 4E 10 A6 00 00 40 11 E5 09 C0 A8 01 A0 C0 A8

0020: 01 FF 00 89 00 89 00 3A AA 2F 80 D8 01 10 00 01

0030: 00 00 00 00 00 00 20 45 44 45 42 45 4A 46 48 46

0040: 46 43 41 43 41 43 41 43 41 43 41 43 41 43 41 43

0050: 41 43 41 43 41 41 41 00 00 20 00 01

-----------------------------

(3) tse 12.1版本已经可以支持IEEE 1588V2精密时间协议(PTP)协议。

IEEE1588的全称是“网络测量和控制系统的精密时钟同步协议标准”,是通用的提升网络系统定时同步能力的规范,在起草过程中主要参考以太网来编制,使分布式通信网络能够具有严格的定时同步,并且应用于工业自动化系统。基本构思是通过硬件和软件将网络设备(客户机)的内时钟与主控机的主时钟实现同步,提供同步建立时间小于10μs的运用,与未执行IEEE1588协议的以太网延迟时间1,000μs相比,整个网络的定时同步指标有显著的改善。