2021-09-08 13:12:03 索炜达电子 1179

项目编号:E866

文件大小:28M

源码说明:带中文注释

开发环境:Verilog

简要概述

EDA课程设计期末大作业-基于FPGA的数字频率计设计

EDA 技术的发展,改变了传统的电子设计方法。FPGA 等大规模可编程逻辑器件的广泛应用,使电子设计变得和软件编程一样方便快捷。电子设计技术的进步,

也改变了传统频率计的设计方法。随着数字电路技术的发展,以脉冲计数法为基础衍生出各种改进型的数字测频方法,在测量精度、测量响应的快速性等方面都有了很大提高。 频率计的核心测频模块采用了基于 FPGA 大规模可编程逻辑器件的 EDA 设计技术,依据自上而下的设计方法,将测频模块按照实现功能的不同划分成了多个子模块,用 Verilog 程序实现了每个子模块的功能,最后通过顶层设计文件中的元件例化语句将各个模块连接起来形成了测频模块的完整 Verilog 程序设计。

设计报告:

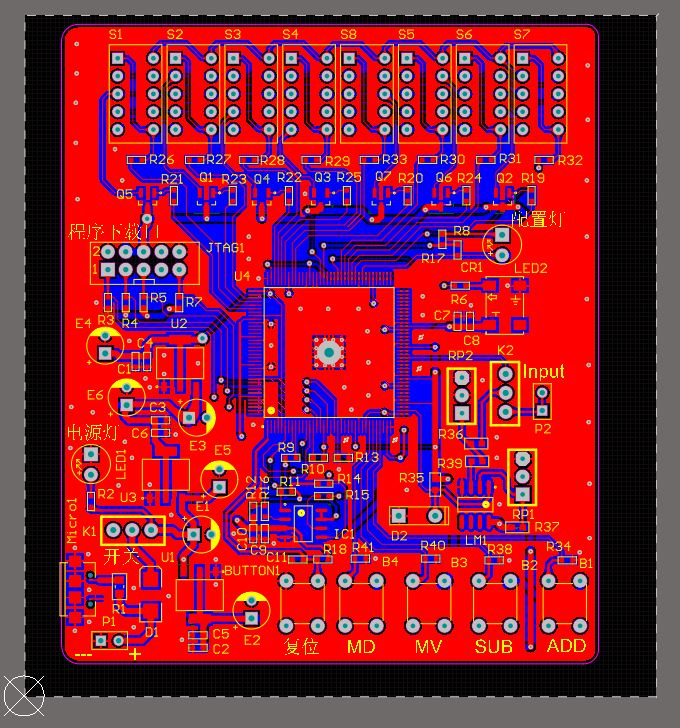

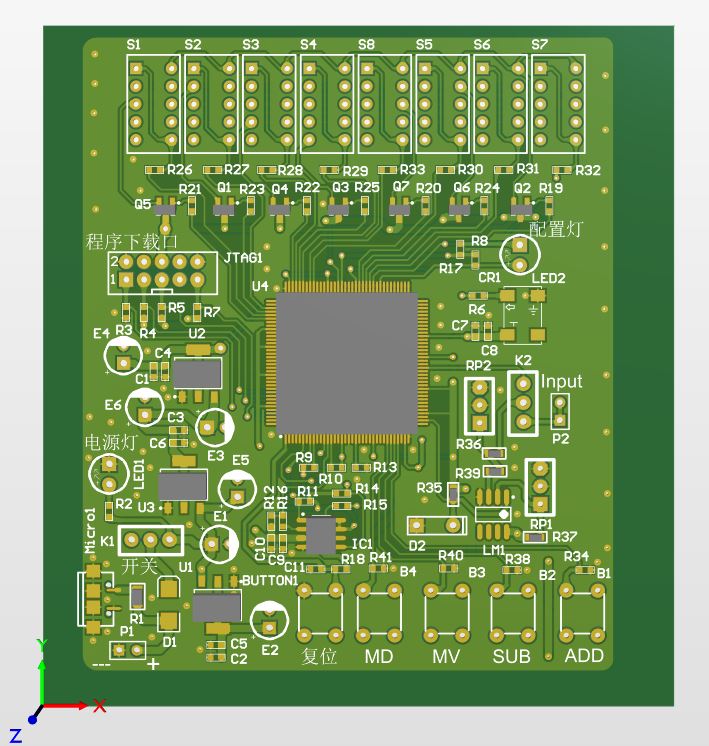

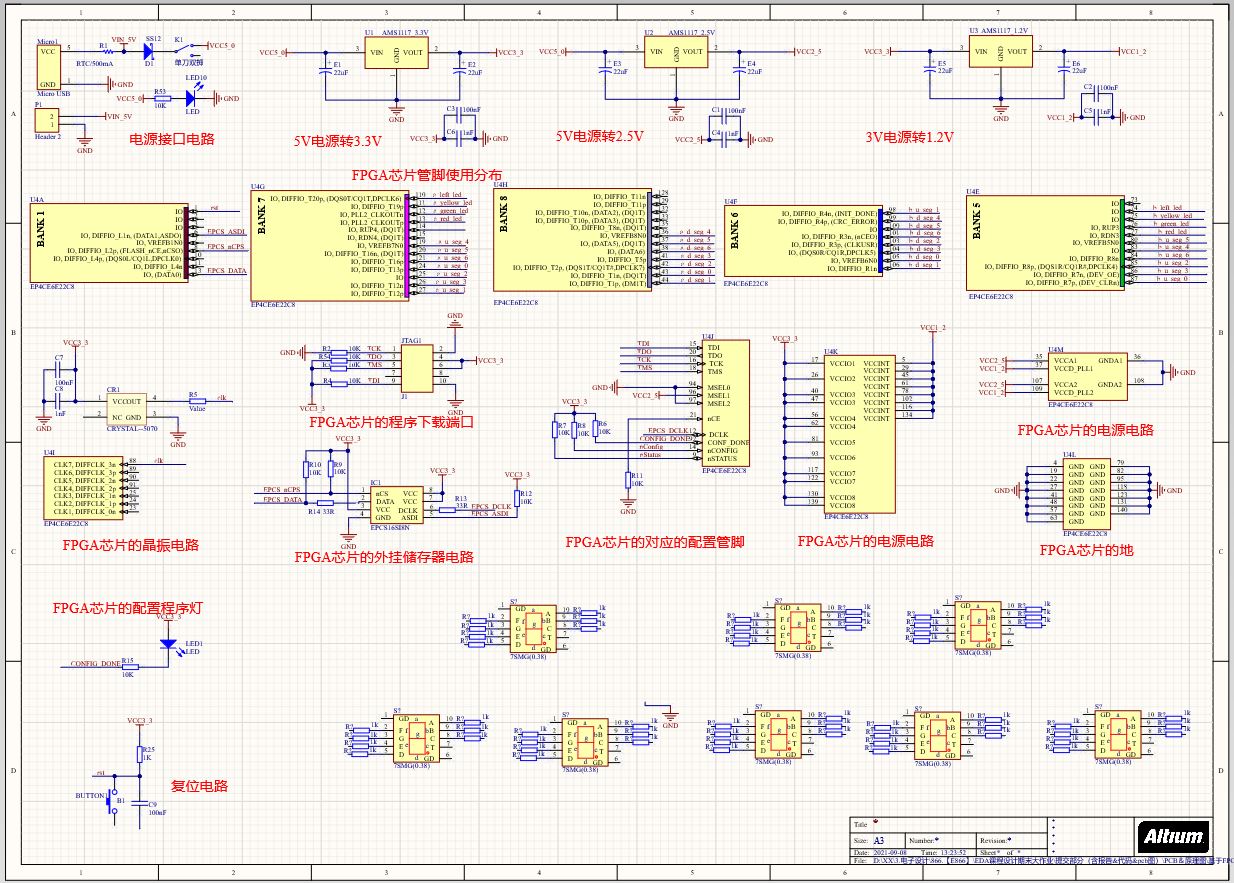

电路板和原理图:

仿真结果:

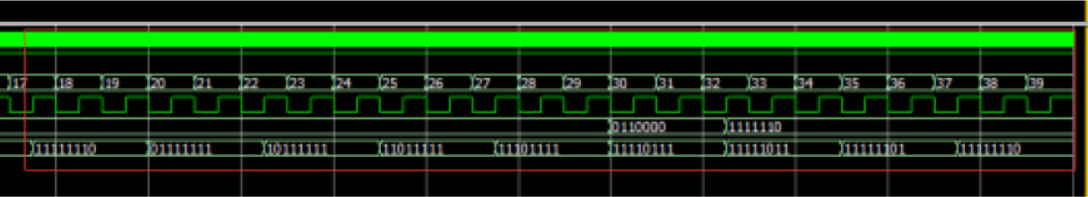

仿真文件中模拟输入了一个1Khz的方波,用于频率测量,下面按步骤讲解如何进行仿真

图4.2 仿真结果

结论:将值按照数码管译码表对比,动态扫描显示的数值为1000hz,证明系统级仿真正确,系统仿真正确。

目录│文件列表:

└ EDA课程设计期末大作业

└ 提交部分(含报告&代码&pcb图)

│ EDA期末大作业报告书.doc

├ History

│ └ 基于FPGA的数字频率计设计.~(1).SchDoc.Zip

├ module_test

│ ├ fre_indicator

│ │ ├ project

│ │ │ │ div.qip

│ │ │ │ div.v

│ │ │ │ div_bb.v

│ │ │ │ fre_indicator.qpf

│ │ │ │ fre_indicator.qsf

│ │ │ │ fre_indicator.qws

│ │ │ │ fre_indicator_nativelink_simulation.rpt

│ │ │ ├ db

│ │ │ │ │ .cmp.kpt

│ │ │ │ │ add_sub_7pc.tdf

│ │ │ │ │ add_sub_8pc.tdf

│ │ │ │ │ alt_u_div_3tf.tdf

│ │ │ │ │ fre_indicator.(0).cnf.cdb

│ │ │ │ │ fre_indicator.(0).cnf.hdb

│ │ │ │ │ fre_indicator.(1).cnf.cdb

│ │ │ │ │ fre_indicator.(1).cnf.hdb

│ │ │ │ │ fre_indicator.(2).cnf.cdb

│ │ │ │ │ fre_indicator.(2).cnf.hdb

│ │ │ │ │ fre_indicator.(3).cnf.cdb

│ │ │ │ │ fre_indicator.(3).cnf.hdb

│ │ │ │ │ fre_indicator.(4).cnf.cdb

│ │ │ │ │ fre_indicator.(4).cnf.hdb

│ │ │ │ │ fre_indicator.(5).cnf.cdb

│ │ │ │ │ fre_indicator.(5).cnf.hdb

│ │ │ │ │ fre_indicator.(6).cnf.cdb

│ │ │ │ │ fre_indicator.(6).cnf.hdb

│ │ │ │ │ fre_indicator.(7).cnf.cdb

│ │ │ │ │ fre_indicator.(7).cnf.hdb

│ │ │ │ │ fre_indicator.asm.qmsg

│ │ │ │ │ fre_indicator.asm.rdb

│ │ │ │ │ fre_indicator.asm_labs.ddb

│ │ │ │ │ fre_indicator.cbx.xml

│ │ │ │ │ fre_indicator.cmp.bpm

│ │ │ │ │ fre_indicator.cmp.cdb

│ │ │ │ │ fre_indicator.cmp.hdb

│ │ │ │ │ fre_indicator.cmp.idb

│ │ │ │ │ fre_indicator.cmp.logdb

│ │ │ │ │ fre_indicator.cmp.rdb

│ │ │ │ │ fre_indicator.cmp_merge.kpt

│ │ │ │ │ fre_indicator.cycloneive_io_sim_cache.45um_ff_1200mv_0c_fast.hsd

│ │ │ │ │ fre_indicator.cycloneive_io_sim_cache.45um_ss_1200mv_0c_slow.hsd

│ │ │ │ │ fre_indicator.cycloneive_io_sim_cache.45um_ss_1200mv_85c_slow.hsd

│ │ │ │ │ fre_indicator.db_info

│ │ │ │ │ fre_indicator.eda.qmsg

│ │ │ │ │ fre_indicator.fit.qmsg

│ │ │ │ │ fre_indicator.hier_info

│ │ │ │ │ fre_indicator.hif

│ │ │ │ │ fre_indicator.ipinfo

│ │ │ │ │ fre_indicator.lpc.html

│ │ │ │ │ fre_indicator.lpc.rdb

│ │ │ │ │ fre_indicator.lpc.txt

│ │ │ │ │ fre_indicator.map.ammdb

│ │ │ │ │ fre_indicator.map.bpm

│ │ │ │ │ fre_indicator.map.cdb

│ │ │ │ │ fre_indicator.map.hdb

│ │ │ │ │ fre_indicator.map.kpt

│ │ │ │ │ fre_indicator.map.logdb

│ │ │ │ │ fre_indicator.map.qmsg

│ │ │ │ │ fre_indicator.map.rdb

│ │ │ │ │ fre_indicator.map_bb.cdb

│ │ │ │ │ fre_indicator.map_bb.hdb

│ │ │ │ │ fre_indicator.map_bb.logdb

│ │ │ │ │ fre_indicator.npp.qmsg

│ │ │ │ │ fre_indicator.pre_map.hdb

│ │ │ │ │ fre_indicator.pti_db_list.ddb

│ │ │ │ │ fre_indicator.root_partition.map.reg_db.cdb

│ │ │ │ │ fre_indicator.routing.rdb

│ │ │ │ │ fre_indicator.rtlv.hdb

│ │ │ │ │ fre_indicator.rtlv_sg.cdb

│ │ │ │ │ fre_indicator.rtlv_sg_swap.cdb

│ │ │ │ │ fre_indicator.sgate.nvd

│ │ │ │ │ fre_indicator.sgate_sm.nvd

│ │ │ │ │ fre_indicator.sgdiff.cdb

│ │ │ │ │ fre_indicator.sgdiff.hdb

│ │ │ │ │ fre_indicator.sld_design_entry.sci

│ │ │ │ │ fre_indicator.sld_design_entry_dsc.sci

│ │ │ │ │ fre_indicator.smart_action.txt

│ │ │ │ │ fre_indicator.sta.qmsg

│ │ │ │ │ fre_indicator.sta.rdb

│ │ │ │ │ fre_indicator.sta_cmp.8_slow_1200mv_85c.tdb

│ │ │ │ │ fre_indicator.tiscmp.fastest_slow_1200mv_0c.ddb

│ │ │ │ │ fre_indicator.tiscmp.fastest_slow_1200mv_85c.ddb

│ │ │ │ │ fre_indicator.tiscmp.fast_1200mv_0c.ddb

│ │ │ │ │ fre_indicator.tiscmp.slow_1200mv_0c.ddb

│ │ │ │ │ fre_indicator.tiscmp.slow_1200mv_85c.ddb

│ │ │ │ │ fre_indicator.tis_db_list.ddb

│ │ │ │ │ fre_indicator.vpr.ammdb

│ │ │ │ │ logic_util_heursitic.dat

│ │ │ │ │ lpm_divide_eqt.tdf

│ │ │ │ │ prev_cmp_fre_indicator.qmsg

│ │ │ │ └ sign_div_unsign_6ai.tdf

│ │ │ ├ greybox_tmp

│ │ │ │ │ cbx_args.txt

│ │ │ ├ incremental_db

│ │ │ │ │ README

│ │ │ │ └ compiled_partitions

│ │ │ │ │ fre_indicator.db_info

│ │ │ │ │ fre_indicator.root_partition.cmp.ammdb

│ │ │ │ │ fre_indicator.root_partition.cmp.cdb

│ │ │ │ │ fre_indicator.root_partition.cmp.dfp

│ │ │ │ │ fre_indicator.root_partition.cmp.hdb

│ │ │ │ │ fre_indicator.root_partition.cmp.logdb

│ │ │ │ │ fre_indicator.root_partition.cmp.rcfdb

│ │ │ │ │ fre_indicator.root_partition.map.cdb

│ │ │ │ │ fre_indicator.root_partition.map.dpi

│ │ │ │ │ fre_indicator.root_partition.map.hbdb.cdb

│ │ │ │ │ fre_indicator.root_partition.map.hbdb.hb_info

│ │ │ │ │ fre_indicator.root_partition.map.hbdb.hdb

│ │ │ │ │ fre_indicator.root_partition.map.hbdb.sig

│ │ │ │ │ fre_indicator.root_partition.map.hdb

│ │ │ │ └ fre_indicator.root_partition.map.kpt

│ │ │ ├ output_files

│ │ │ │ │ fre_indicator.asm.rpt

│ │ │ │ │ fre_indicator.done

│ │ │ │ │ fre_indicator.eda.rpt

│ │ │ │ │ fre_indicator.fit.rpt

│ │ │ │ │ fre_indicator.fit.smsg

│ │ │ │ │ fre_indicator.fit.summary

│ │ │ │ │ fre_indicator.flow.rpt

│ │ │ │ │ fre_indicator.jdi

│ │ │ │ │ fre_indicator.map.rpt

│ │ │ │ │ fre_indicator.map.summary

│ │ │ │ │ fre_indicator.pin

│ │ │ │ │ fre_indicator.sof

│ │ │ │ │ fre_indicator.sta.rpt

│ │ │ │ └ fre_indicator.sta.summary

│ │ │ └ simulation

│ │ │ └ modelsim

│ │ │ │ fre_indicator.sft

│ │ │ │ fre_indicator.vho

│ │ │ │ fre_indicator.vo

│ │ │ │ fre_indicator.vt

│ │ │ │ fre_indicator.vt.bak

│ │ │ │ fre_indicator_8_1200mv_0c_slow.vho

│ │ │ │ fre_indicator_8_1200mv_0c_slow.vo

│ │ │ │ fre_indicator_8_1200mv_0c_vhd_slow.sdo

│ │ │ │ fre_indicator_8_1200mv_0c_v_slow.sdo

│ │ │ │ fre_indicator_8_1200mv_85c_slow.vho

│ │ │ │ fre_indicator_8_1200mv_85c_slow.vo

│ │ │ │ fre_indicator_8_1200mv_85c_vhd_slow.sdo

│ │ │ │ fre_indicator_8_1200mv_85c_v_slow.sdo

│ │ │ │ fre_indicator_8_1200mv_85c_v_slow.sdo_typ.csd

│ │ │ │ fre_indicator_min_1200mv_0c_fast.vho

│ │ │ │ fre_indicator_min_1200mv_0c_fast.vo

│ │ │ │ fre_indicator_min_1200mv_0c_vhd_fast.sdo

│ │ │ │ fre_indicator_min_1200mv_0c_v_fast.sdo

│ │ │ │ fre_indicator_modelsim.xrf

│ │ │ │ fre_indicator_run_msim_gate_verilog.do

│ │ │ │ fre_indicator_run_msim_rtl_verilog.do

│ │ │ │ fre_indicator_run_msim_rtl_verilog.do.bak