2021-10-03 18:46:45 索炜达电子 868

项目编号:E1359

文件大小:8.89M

源码说明:带中文注释

开发环境:Verilog

简要概述:

总体陈述

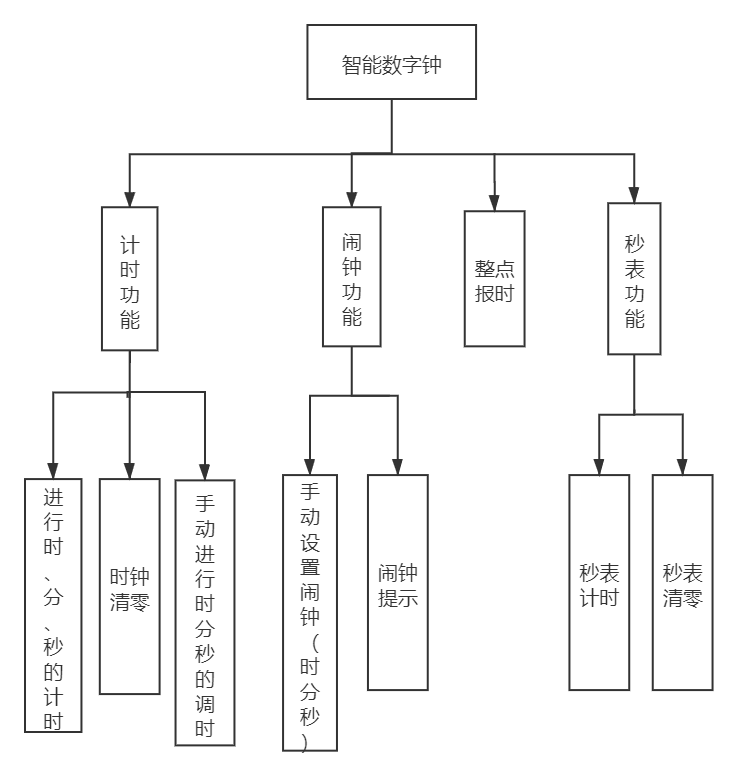

在老师所给的十个大作业选题中,我选择了智能数字钟。对于智能数字钟而言,它需要有哪些功能呢?首先是最基本的显示时间,既然有显示时间,那就应该要可以调时间。除此之外,数字钟应该还应该有闹钟,所以我又给加上了闹钟功能,既可以设置闹钟又可以在到闹钟点的时候给出闹钟提示。还有,整点报时应该也要有。最后,数字秒表的功能也是智能数字钟应该有的功能。综上所述,我设计的智能数字钟的功能如下:

-能进行时、分、秒计时的数字钟(由于实验室的FPGA的板子只有四个数码管,实际程序中时、分用数码管显示,秒用led灯显示,一秒闪一下)

-该数字钟能时钟清零

-该数字钟能对时、分、秒进行手动调时以校准时间

-该数字钟能够手动设置闹钟(也是分别对时、分、秒进行设置)

-该数字到闹钟设置的点后能够给出提示(由于不知道实验室中的FPGA的蜂鸣器的引脚,改用led灯进行提示,闹钟的led灯会在到闹钟点的时候亮是十五秒后自动关闭,和我们手机一样)

-该数字钟能够整点报时(在到达整点的时候进行报时,同闹钟一样,用led灯进行提示,整点报时的led灯在到达整点的时候亮灯十秒)

-该数字钟能进行秒表功能,用户可以使用该数字钟进行秒表计时间(用四个数码管进行显示,最多9999秒,之后清零)

-该数字钟的秒表功能也提供清零功能。(将相当于将秒表清零,用户可重新开始)

经整理后,我设计的智能数字钟整体功能图如下所示:

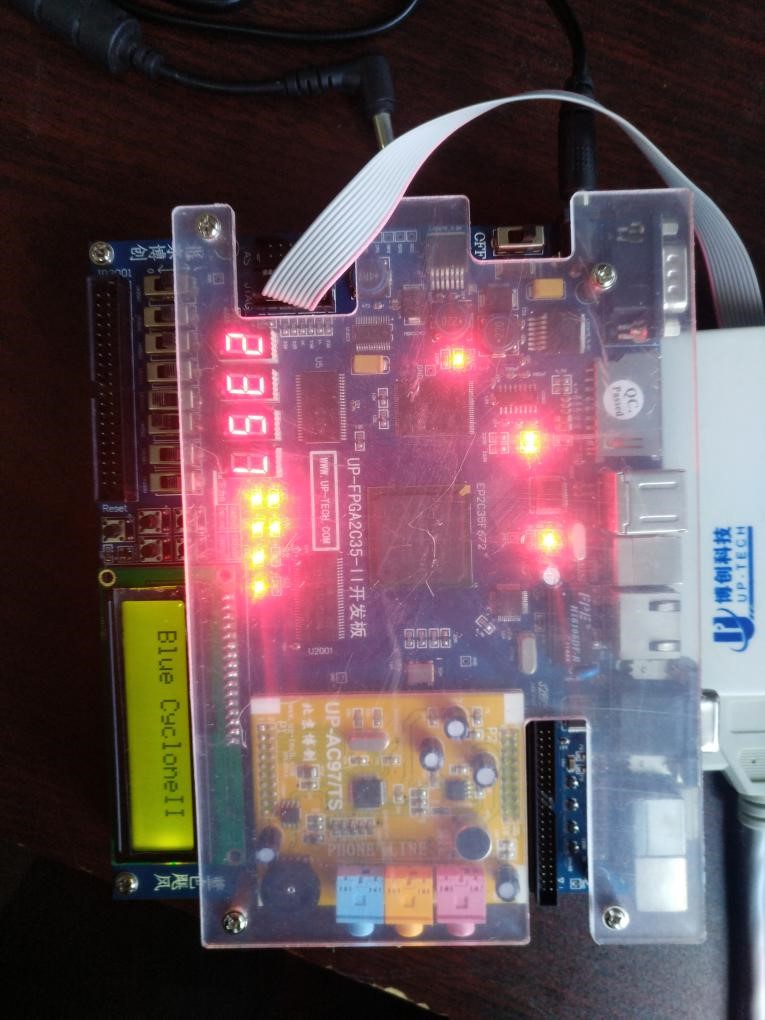

实物图:

目录│文件列表:

└ 基于FPGA的智能数字钟

└ Clock-FPGA

│ FPGA2C35-II开发板蓝色飓风系列管脚分配.txt

│ 开发文档.docx

└ clock

│ alarm_clocking.bsf

│ alarm_clocking.v

│ alarm_clocking.v.bak

│ clockTest.asm.rpt

│ clockTest.bsf

│ clockTest.done

│ clockTest.eda.rpt

│ clockTest.fit.rpt

│ clockTest.fit.smsg

│ clockTest.fit.summary

│ clockTest.flow.rpt

│ clockTest.jdi

│ clockTest.map.rpt

│ clockTest.map.summary

│ clockTest.mif_update.rpt

│ clockTest.pin

│ clockTest.pof

│ clockTest.qpf

│ clockTest.qsf

│ clockTest.qws

│ clockTest.sof

│ clockTest.sta.rpt

│ clockTest.sta.summary

│ clockTest.tan.rpt

│ clockTest.tan.summary

│ clockTest.v

│ clockTest.v.bak

│ clockTest_assignment_defaults.qdf

│ clockTest_nativelink_simulation.rpt

│ count.bsf

│ count.v

│ count.v.bak

│ decide_option.bsf

│ decide_option.v

│ decide_option.v.bak

│ fenPIN.bsf

│ fenPIN.v

│ fenPIN.v.bak