2021-08-22 17:39:46 索炜达电子 965

项目编号:E439

文件大小:22M

源码说明:带中文注释

开发环境:vivido

简要概述:

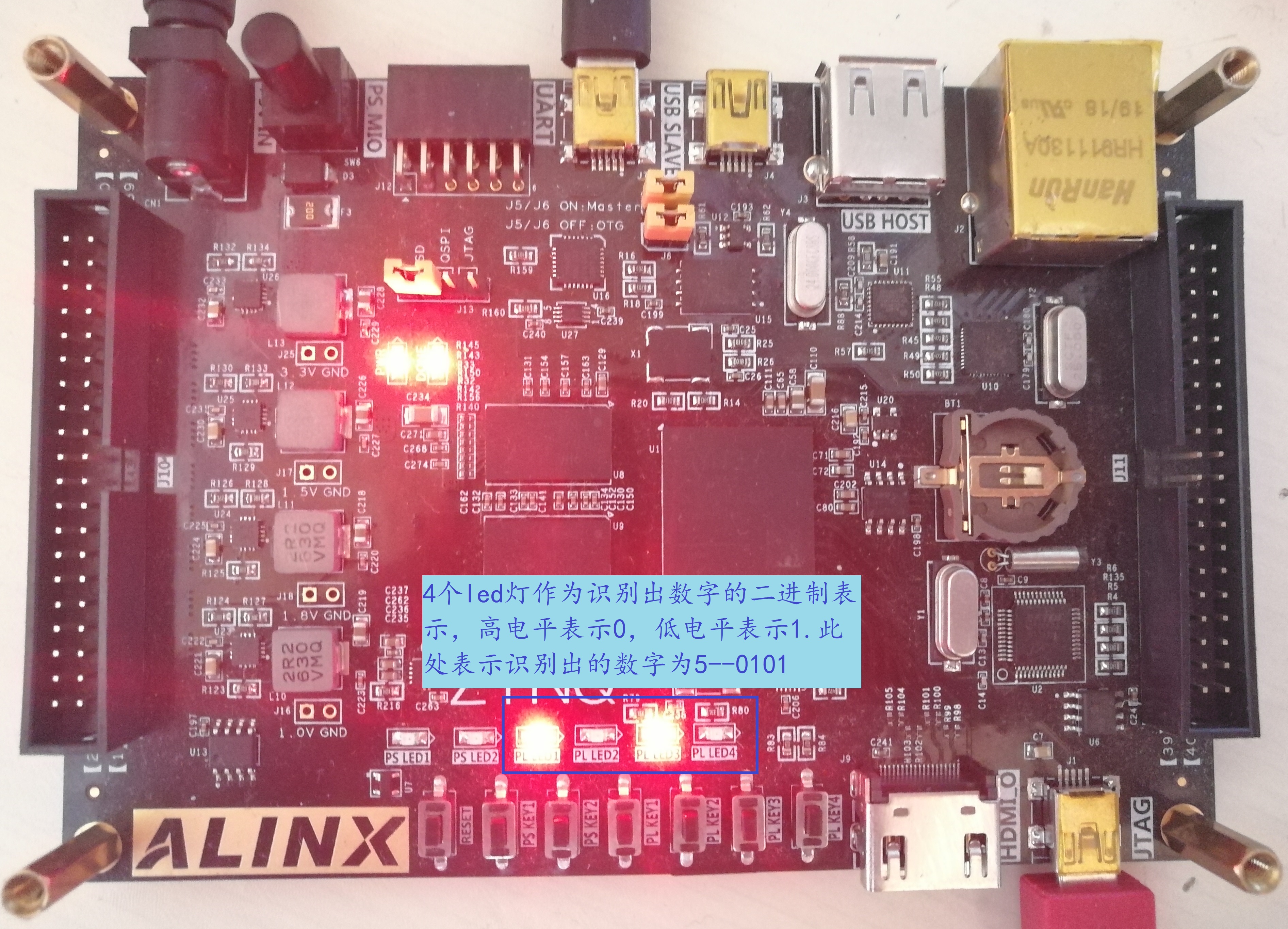

使用FPGA vivido根据数字的图像特征给数字加边界,并识别数字大小

该工程的识别原理和代码讲解可以参考基于FPGA的数字识别实现,同时感谢这位博主的分享教程。该工程也是参考这位博主的教程完成的。

digital_identify文件夹为vivido工程文件夹

imgs文件夹包含工程中使用到的640*480的0~9源图片、仿真结果、加边界后的数字图片,以及上板测试的结果。

matlab文件夹包含了将图片转为数字文件、显示加边界后的数字文件用到的matlab代码。

digital_identify模块为顶层模块-

serial_data_gen模块实现数据的读入,使用rom IP核初始化matlab生成的.coe数据文件

edge_check模块实现查找数字边界值

edge_disp模块实现输出加边界后的数据

num_recog模块实现数字的识别

软件环境 vivido 2018.3 matlab 2018b

硬件环境 zynq xc7z020clg400-2

目录│文件列表:

└ fpga-digital-recognition

├ digital_identify

│ │ digital_identify.xpr

│ │ vivado.jou

│ │ vivado.log

│ ├ digital_identify.cache

│ │ └ wt

│ │ │ gui_handlers.wdf

│ │ │ java_command_handlers.wdf

│ │ │ project.wpc

│ │ │ webtalk_pa.xml

│ │ └ xsim.wdf

│ ├ digital_identify.hw

│ │ │ digital_identify.lpr

│ │ └ hw_1

│ │ └ hw.xml

│ ├ digital_identify.ip_user_files

│ │ │ README.txt

│ │ ├ ip

│ │ │ └ rom

│ │ │ │ rom.veo

│ │ │ └ rom.vho

│ │ ├ ipstatic

│ │ │ └ simulation

│ │ │ └ blk_mem_gen_v8_4.v

│ │ ├ mem_init_files

│ │ │ │ num_data.coe

│ │ │ │ num_data0.coe

│ │ │ │ num_data1.coe

│ │ │ │ num_data2.coe

│ │ │ │ num_data3.coe

│ │ │ │ num_data5.coe

│ │ │ │ num_data8.coe

│ │ │ │ rom.mif

│ │ │ └ summary.log

│ │ └ sim_scripts

│ │ └ rom

│ │ │ README.txt

│ │ ├ activehdl

│ │ │ │ compile.do

│ │ │ │ file_info.txt

│ │ │ │ glbl.v

│ │ │ │ num_data5.coe

│ │ │ │ README.txt

│ │ │ │ rom.mif

│ │ │ │ rom.sh

│ │ │ │ rom.udo

│ │ │ │ simulate.do

│ │ │ │ summary.log

│ │ │ └ wave.do

│ │ ├ ies

│ │ │ │ file_info.txt

│ │ │ │ glbl.v

│ │ │ │ num_data5.coe

│ │ │ │ README.txt

│ │ │ │ rom.mif

│ │ │ │ rom.sh

│ │ │ │ run.f

│ │ │ └ summary.log

│ │ ├ modelsim

│ │ │ │ compile.do

│ │ │ │ file_info.txt

│ │ │ │ glbl.v

│ │ │ │ num_data5.coe

│ │ │ │ README.txt

│ │ │ │ rom.mif

│ │ │ │ rom.sh

│ │ │ │ rom.udo

│ │ │ │ simulate.do

│ │ │ │ summary.log

│ │ │ └ wave.do

│ │ ├ questa

│ │ │ │ compile.do

│ │ │ │ elaborate.do

│ │ │ │ file_info.txt

│ │ │ │ glbl.v

│ │ │ │ num_data5.coe

│ │ │ │ README.txt

│ │ │ │ rom.mif

│ │ │ │ rom.sh

│ │ │ │ rom.udo

│ │ │ │ simulate.do

│ │ │ │ summary.log

│ │ │ └ wave.do

│ │ ├ riviera

│ │ │ │ compile.do

│ │ │ │ file_info.txt

│ │ │ │ glbl.v

│ │ │ │ num_data5.coe

│ │ │ │ README.txt

│ │ │ │ rom.mif

│ │ │ │ rom.sh

│ │ │ │ rom.udo

│ │ │ │ simulate.do

│ │ │ │ summary.log

│ │ │ └ wave.do

│ │ ├ vcs

│ │ │ │ file_info.txt

│ │ │ │ glbl.v

│ │ │ │ num_data5.coe

│ │ │ │ README.txt

│ │ │ │ rom.mif

│ │ │ │ rom.sh

│ │ │ │ simulate.do

│ │ │ └ summary.log

│ │ ├ xcelium

│ │ │ │ file_info.txt

│ │ │ │ glbl.v

│ │ │ │ num_data5.coe

│ │ │ │ README.txt

│ │ │ │ rom.mif

│ │ │ xsim.ini.bak

│ │ │ xvlog.log

│ │ │ xvlog.pb

│ │ └ xsim.dir

│ │ ├ rom_test_tb_behav

│ │ │ │ Compile_Options.txt

│ │ │ │ TempBreakPointFile.txt

│ │ │ │ xsim.dbg

│ │ │ │ xsim.mem

│ │ │ │ xsim.reloc

│ │ │ │ xsim.rlx

│ │ │ │ xsim.rtti

│ │ │ │ xsim.svtype

│ │ │ │ xsim.type

│ │ │ │ xsim.xdbg

│ │ │ │ xsimcrash.log

│ │ │ │ xsimk.exe

│ │ │ │ xsimkernel.log

│ │ │ │ xsimSettings.ini

│ │ │ ├ obj

│ │ │ │ │ xsim_0.win64.obj

│ │ │ │ │ xsim_1.c

│ │ │ │ └ xsim_1.win64.obj

│ │ │ └ webtalk

│ │ │ │ .xsim_webtallk.info

│ │ │ │ usage_statistics_ext_xsim.html

│ │ │ │ usage_statistics_ext_xsim.wdm

│ │ │ │ usage_statistics_ext_xsim.xml

│ │ │ └ xsim_webtalk.tcl

│ │ ├ top_tb_behav

│ │ │ │ Compile_Options.txt

│ │ │ │ TempBreakPointFile.txt

│ │ │ │ xsim.dbg

│ │ │ │ xsim.mem

│ │ │ │ xsim.reloc

│ │ │ │ xsim.rlx

│ │ │ │ xsim.rtti

│ │ │ │ xsim.svtype

│ │ │ │ xsim.type

│ │ │ │ xsim.xdbg

│ │ │ │ xsimcrash.log

│ │ │ │ xsimk.exe

│ │ │ │ xsimkernel.log

│ │ │ │ xsimSettings.ini

│ │ │ ├ obj

│ │ │ │ │ xsim_0.win64.obj

│ │ │ │ │ xsim_1.c

│ │ │ │ └ xsim_1.win64.obj

│ │ │ └ webtalk

│ │ │ │ .xsim_webtallk.info

│ │ │ │ usage_statistics_ext_xsim.html

│ │ │ │ usage_statistics_ext_xsim.wdm

│ │ │ │ usage_statistics_ext_xsim.xml

│ │ │ └ xsim_webtalk.tcl

│ │ └ xil_defaultlib

│ │ │ digital_identify.sdb

│ │ │ edge_check.sdb

│ │ │ edge_disp.sdb

│ │ │ glbl.sdb

│ │ │ num_recog.sdb

│ │ │ rom.sdb

│ │ │ rom_test_tb.sdb

│ │ │ serial_data_gen.sdb

│ │ │ top_tb.sdb

│ │ └ xil_defaultlib.rlx

│ └ digital_identify.srcs

│ ├ constrs_1

│ │ └ new

│ │ └ system.xdc

│ ├ sim_1

│ │ └ new

│ │ │ rom_test_tb.v

│ │ └ top_tb.v

│ └ sources_1

│ ├ ip

│ │ └ rom

│ │ │ rom.dcp

│ │ │ rom.mif

│ │ │ rom.veo

│ │ │ rom.vho

│ │ │ rom.xci

│ │ │ rom.xml

│ │ │ rom_ooc.xdc

│ │ │ rom_sim_netlist.v

│ │ │ rom_sim_netlist.vhdl

│ │ │ rom_stub.v

│ │ │ rom_stub.vhdl

│ │ │ summary.log

│ │ ├ doc

│ │ │ └ blk_mem_gen_v8_4_changelog.txt

│ │ ├ hdl

│ │ │ └ blk_mem_gen_v8_4_vhsyn_rfs.vhd

│ │ ├ misc

│ │ │ └ blk_mem_gen_v8_4.vhd

│ │ ├ sim

│ │ │ └ rom.v

│ │ ├ simulation

│ │ │ └ blk_mem_gen_v8_4.v

│ │ └ synth

│ │ └ rom.vhd

│ └ new

│ │ digital_identify.v

│ │ edge_check.v

│ │ edge_disp.v

│ │ num_recog.v

│ └ serial_data_gen.v

├ imgs

│ │ 0.png

│ │ 1.png

│ │ 2.png

│ │ 3.png

│ │ 4.png

│ │ 5.png

│ │ 6.png

│ │ 7.png

│ │ 8.png

│ │ 9.png

│ │ 上板测试结果.jpg

│ └ 仿真结果和加边界图片.docx

└ matlab

│ numRecognition.m

└ showimg.m